PAMS Technical Documentation RAE-2 Series PDA

# Chapter 5 BS1 PDA Module

Section 02/99 Copyright © 1999. Nokia Mobile Phones. All Rights Reserved.

| Amendment<br>Number |       | Inserted By | Comments |

|---------------------|-------|-------------|----------|

|                     | 02/99 | OJuntune    | Original |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

BS1

# **CONTENTS – PDA module BS1**

# Page No

| Introduction                     | 5 – 4  |

|----------------------------------|--------|

| Technical Summary                | 5 – 4  |

| Electronics                      | 5 – 5  |

| Interconnection Diagram          | 5 – 6  |

| DC Characteristics               | 5 – 7  |

| AC Characteristics               | 5 – 8  |

| External Signals and Connections | 5 – 8  |

| UI flex connector                | 5 – 9  |

| Board to board connector signals | 5 – 12 |

| System connector pads            | 5 – 16 |

| Audio connector pads             | 5 – 17 |

| Backup battery                   | 5 – 17 |

| Internal Signals and Connections | 5 – 18 |

| Functional Description           | 5 – 20 |

| Power Unit                       | 5 – 20 |

| Input filter                     | 5 – 21 |

| Linear regulator V28             | 5 – 21 |

| Linear regulator V28_1,_2,_3     | 5 – 21 |

| Switchmode regulator V17         | 5 – 21 |

| Backup battery                   | 5 – 21 |

| Reset and power management       | 5 – 22 |

| PDA CPU                          | 5 – 22 |

| I/O Signals                      | 5 – 24 |

| Memories                         | 5 – 25 |

| DRAM memory                      | 5 – 25 |

| Flash memory                     | 5 – 25 |

| External Serial Interface        | 5 – 26 |

| IR-Transceiver                   | 5 – 26 |

| Handsfree loudspeaker            | 5 – 26 |

| Keyboard                         | 5 – 26 |

|                                  | 5 – 28 |

| Testpoints                       | 5 – 30 |

# Introduction

The function of the BS1 PDA module in RAE–2 Communicator device is to run all applications that utilize the PDA LCD display of the device. The GEOS operating system is applied on a 486 based PDA module platform. This processing platform utilizes the communicator–type user interface which is accessible when the RAE–2 is opened.

# **Technical Summary**

The BS1 PDA module consists of a printed circuit board with a CPU, two kinds of memories, a Power unit, HF amplifier circuitry, and an IR-transceiver.

The PDA module is assembled on a single 8–layer printed circuit board. All components are assembled on one single side. The other side is reserved for keyboard keypads.

Serial ports, DMA– and LCD controller for timers are integrated in the CPU. The operating system is GEOS supplied by Geoworks.

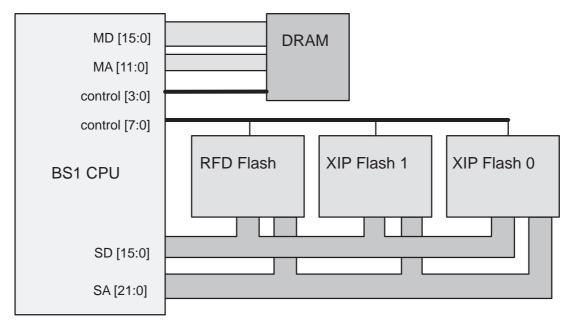

The BS1 module includes three non–volatile Flash memories which are used for two kind of purposes. XIP (executed in place) memory is used for program file storage and RFD (resident flash disk) memory is writeable for user data.

One DRAM Memory is used for the code execution and for the volatile storage of the internal run–time system data.

Both memory types (DRAM and Flash) have their own address– and data bus, routed directly from the CPU.

| Memory type | Amount (Bytes) |

|-------------|----------------|

| Flash (XIP) | 4M             |

| Flash (RFD) | 2M             |

| DRAM        | 2M             |

The BS1 PWRU block regulates the PDA module power and controls the power-up and -down. After a battery has been connected, the PWRU gives the CPU system voltage and releases the reset as fast as possible after which the CPU SW has full power management control. The PWRU also generates and controls the voltages that the PDA LCD uses. The PDA has a rechargeable back–up battery which the PWRU block charges when the main battery is connected. The VBACK voltage is normally always available for real time clock. Power is fed from the battery through the CMT module to the PDA PWRU. The PWRU has a filter in battery line to reduce interference from the CMT module. The PWRU provides

A/D converter readings of the battery voltage and temperature via a parallel interface to the CPU. Many PWRU items can be controlled by register writing or directly via pin. The system voltage is always present until battery voltage drops below 3.0V.

## **Electronics**

The following sections of circuitry are included on the BS1:

| Function               |

|------------------------|

| PWRU Power supply unit |

| PDA CPU                |

| IR transceiver         |

| DRAM memory            |

| Flash memory           |

| HF Amplifier           |

| QWERTY Keyboard pads   |

BS1

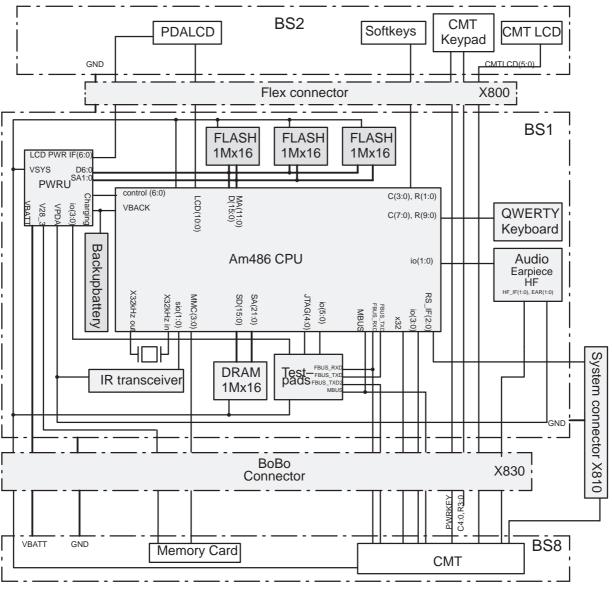

## **Interconnection Diagram**

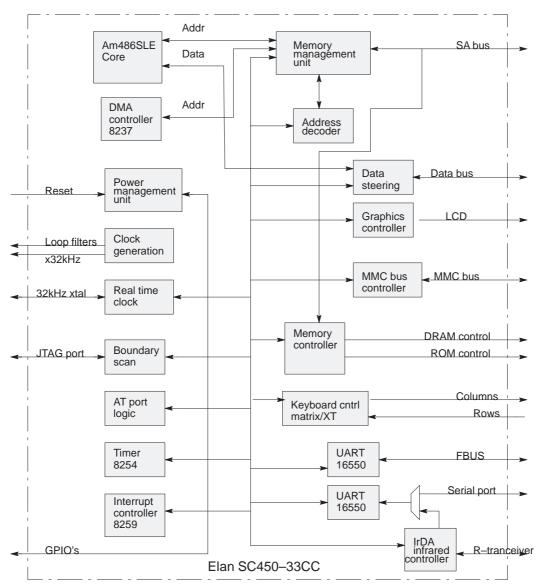

Figure 1. BS 1 PDA block in RAE–2 product NOTE: All modules have same ground.

## **DC Characteristics**

| Pin /<br>Conn.     | Line Symbol | Minimum | Nominal | Maximum | Unit | Notes                                                        |

|--------------------|-------------|---------|---------|---------|------|--------------------------------------------------------------|

| 1,2,3,4,5/<br>X830 | VBATT       | 3.0     | 3.6     | 4.1     | VDC  | Battery voltage,<br>SW limit                                 |

| 1,2,3,4,5/<br>X830 |             |         |         | 900     | mA   | Current                                                      |

| E307               | VBACK       | 2.4     | 3.0     | 3.15    | VDC  | Backup battery voltage                                       |

|                    |             | 0.4     | 0.5     | 0.7     | mA   | Charge current                                               |

|                    |             |         | 0.25    | 0.4     | mA   | Quiescent current in suspend mode                            |

| E312               | VSYS        | 2.75    | 2.8     | 2.85    | VDC  | System voltage                                               |

|                    |             | 0.050   | 300     | 450     | mA   | Current                                                      |

| E300               | V17_OUT     | 17.1    | 19.4    | 21.6    | VDC  | LCD Biasing volt-<br>age, NOTE1                              |

|                    |             | 19.0    | 19.8    | 20.6    | VDC  | LCD Biasing volt-<br>age, at +20C                            |

|                    |             |         | 2       | 5       | mA   | Current                                                      |

| 7/X800 V17_i       | V17_i1      | 15.8    | 17.9    | 19.9    | VDC  | LCD intermediate<br>voltage1<br>(12/13xV17_OUT<br>). NOTE1   |

|                    |             | 17.5    | 18.3    | 19.0    | VDC  | at +20C                                                      |

|                    |             |         |         | 4       | mA   | Current                                                      |

| 8/X800 V17_i2      | V17_i2      | 14.4    | 16.4    | 18.3    | VDC  | LCD intermediate<br>voltage2<br>(11/13xV17_OUT<br>). NOTE1   |

|                    |             | 16.1    | 16.8    | 17.4    | VDC  | at +20C                                                      |

|                    |             |         |         | 4       | mA   | Current                                                      |

| 9/X800             | V17_i3      | 2.6     | 3.0     | 3.3     | VDC  | LCD intermediate<br>voltage3<br>(2/13xV17_OUT).<br>Max range |

|                    |             | 2.9     | 3.0     | 3.2     | VDC  | at +20C                                                      |

|                    |             |         |         | 4       | mA   | Current                                                      |

| 10/X800            | V17_i4      | 1.3     | 1.5     | 1.7     | VDC  | LCD intermediate<br>voltage4<br>(1/13xV17_OUT).<br>NOTE1     |

|                    |             | 1.4     | 1.5     | 1.6     | VDC  | at +20C                                                      |

|                    |             |         |         | 4       | mA   | Current                                                      |

## Table 2. Supply Voltages and Power Consumption

| RAE–2 |  |

|-------|--|

|-------|--|

| BS1 |

|-----|

|-----|

| Pin /<br>Conn. | Line Symbol | Minimum | Nominal | Maximum | Unit | Notes                            |

|----------------|-------------|---------|---------|---------|------|----------------------------------|

| 3/X800         | V28_1       | 2.70    | 2.80    | 2.85    | VDC  | LCD Logic volt-<br>age           |

|                |             |         | 1       | 4       | mA   | Current                          |

| 21/N450        | V28_2       | 2.70    | 2.8     | 2.85    | VDC  | IrDA Logic volt-<br>age          |

|                |             |         | 2       | 4       | mA   | Current                          |

| 46/X830        | V28_3       | 2.75    | 2.8     | 2.85    | VDC  | MMC supply volt-<br>age          |

|                |             | 0.01    | 50      | 100     | mA   | Current                          |

| 16/X830        | VBB         | 2.75    | 2.8     | 2.85    | VDC  | Base Band oper-<br>ating voltage |

|                |             |         |         |         | mA   | Current                          |

Table 2. Supply Voltages and Power Consumption (continued)

NOTE : Complete temperature range

## **AC Characteristics**

|                                      | Minimum | Nominal | Maximum | Unit / Notes                   |

|--------------------------------------|---------|---------|---------|--------------------------------|

| External XTAL                        |         | 32.768  |         | kHz                            |

|                                      |         |         | 20      | ppm, accuracy                  |

| CPU clock                            |         | 33.18   |         | MHz, Rise time<br>1–2ns        |

| Memory bus clock                     |         | 33.18   |         | MHz, Rise time<br>2–3ns        |

| Memory Controller clock              |         | 66.3552 |         | MHz, Rise time<br>1–2ns        |

| MMC clock during data                | 0.2592  |         | 8.294   | Mhz, Rise time<br>2–3ns, NOTE1 |

| MMC clock during identifica-<br>tion |         | 259.2   |         | kHz, Rise time 2–3ns           |

NOTE: Frequency is a multiple of 259.2kHz

# **External Signals and Connections**

This section describes the external electrical connection and interface levels on BS1 module. The electrical interface specifications are collected into tables that cover each connector and defined interface.

| Connector Name           | Code | Notes                             |

|--------------------------|------|-----------------------------------|

| UI flex connector        | X800 | CMT/PDA LCD- and Keyboard signals |

| Board to Board connector | X830 | CMT PDA interface                 |

| System connector pads    | X810 |                                   |

BS1

| Connector Name            | Code                                                                                                                             | Notes                                                      |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| Audio connector pads      | E880, E881,<br>E850, E851                                                                                                        | HF-speaker connection and earpiece connection              |  |  |  |  |  |

| Backup battery holder     | X451                                                                                                                             |                                                            |  |  |  |  |  |

| Testpads                  | E300–E315                                                                                                                        | Testpads "under" battery pack                              |  |  |  |  |  |

| Frame connector pads X840 |                                                                                                                                  | Include manufacturing testpads. Is removed before assembly |  |  |  |  |  |

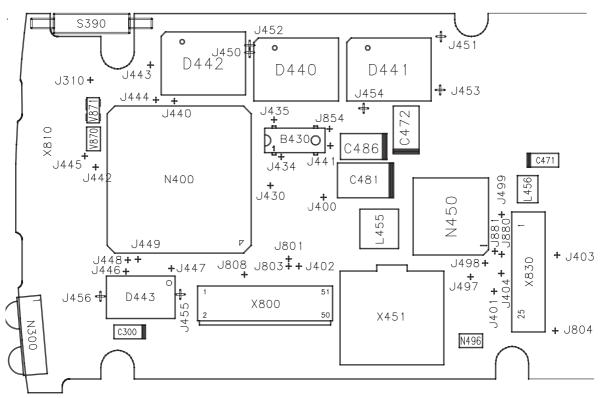

| Testpoints                | J310,<br>J400–J404,<br>J430, J434,<br>J435,<br>J440 – J456,<br>J497 – J499,<br>J801, J803,<br>J804, J808,<br>J854, J880,<br>J881 | Testpoints around the BS1 PCB.                             |  |  |  |  |  |

| Table 3. List of Connectors and testpoints | (continued) |

|--------------------------------------------|-------------|

|--------------------------------------------|-------------|

#### **UI flex connector**

The Interface between the BS2 and BS1 modules comprises a 51–pin flex connector. The connector includes supply voltage for the BS2 module, and required information signals. Signals from the BS8 module are also carried via the flex connector.

| Pin | I/O | Name     | Function                  | Min  | Nom  | Мах  | Unit | Description /<br>Note                                       |

|-----|-----|----------|---------------------------|------|------|------|------|-------------------------------------------------------------|

| 1   |     | GND      | Global Ground             |      |      |      |      |                                                             |

| 2   | I   | LCD_TEMP | PDA LCD Temperature       | 0.2  | 0.9  | 2.5  | VDC  | Voltage range<br>throught the whole<br>temperature range.   |

|     |     |          |                           | 0.2  | 0.9  | 0.91 | VDC  | At +25°C                                                    |

| 3   | 0   | V28_1    | PDA LCD Logic voltage     | 2.70 | 2.80 | 2.85 | VDC  |                                                             |

| 4   | 0   | LCD_ON   | PDA LCD enable            | 2.30 | 2.8  | 2.85 | VDC  | High                                                        |

|     |     |          |                           |      | 0    | 0.4  | VDC  | Low                                                         |

| 5   | 0   | V17_OUT  | PDA LCD Biasing voltage   | 19.0 | 19.8 | 20.6 | VDC  | Range at +20C.<br>Whole range can<br>be seen from<br>table2 |

| 6   |     | GND      | Global Ground             |      |      |      |      |                                                             |

| 7   | 0   | V17_i1   | PDA LCD Intermediate bias | 17.5 | 18.3 | 19.0 | VDC  | Range at +20C.                                              |

| 8   | 0   | V17_i2   | voltage                   | 16.1 | 16.8 | 17.4 | VDC  | Whole range can<br>be seen from                             |

| 9   | 0   | V17_i3   | ]                         | 2.9  | 3.0  | 3.2  | VDC  | table2                                                      |

| 10  | 0   | V17_i4   | ]                         | 1.4  | 1.5  | 1.6  | VDC  |                                                             |

| 11  |     | GND      | Global Ground             |      |      |      |      |                                                             |

Table 4. UI flex Connector X800

|     |     |                                 | e 4. Of fiex confidential  |      |      |      |      |                              |

|-----|-----|---------------------------------|----------------------------|------|------|------|------|------------------------------|

| Pin | I/O | Name                            | Function                   | Min  | Nom  | Мах  | Unit | Description /<br>Note        |

| 12  | 0   | FRM                             | PDA LCD Frame pulse        | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

|     |     |                                 |                            |      | 72   | 100  | Hz   |                              |

|     |     |                                 |                            |      |      |      | %    | Duty cycle                   |

| 13  | 0   | Μ                               | PDA LCD AC Modulation      | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

|     |     |                                 |                            |      | 2.5  | 3.4  | kHz  |                              |

| 14  |     | GND                             | Global Ground              |      |      |      |      |                              |

| 15  | 0   | LC                              | PDA LCD Line pulse         | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

|     |     |                                 |                            |      | 32   | 44.5 | kHz  |                              |

| 16  |     | GND                             | Global Ground              |      |      |      |      |                              |

| 17  | 0   | SCK                             | PDA LCD bus clock          | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

|     |     |                                 |                            |      | 2.3  | 3.2  | MHz  |                              |

| 18  |     | GND                             | Global Ground              |      | 1    | 1    | 1    |                              |

| 19  | 0   | LCDD0                           | PDA LCD Data signal        | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

| 20  | 0   | LCDD1                           | PDA LCD Data signal        | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

| 21  |     | GND                             | Global Ground              |      | 1    | 1    | 1    |                              |

| 22  | 0   | LCDD2                           | PDA LCD Data signal        | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     | -   |                                 | · ·                        |      | 0    | 0.45 | VDC  | Low                          |

| 23  | 0   | LCDD3                           | PDA LCD Data signal        | 2.30 | 2.80 | 2.85 | VDC  | High                         |

|     | Ū   |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

| 24  | 0   | PDA_BL_ON                       | PDA LCD Backlight enabled  | 2.30 | 2.80 | 2.85 | VDC  | High, backlight en-<br>abled |

|     |     |                                 |                            |      | 0    | 0.45 | VDC  | Low                          |

| 25  | 0   | CMT_BL_ON                       | CMT Backlight enabled      | 2.1  | 2.80 | 2.85 | VDC  | High, backlight en-<br>abled |

|     |     |                                 |                            |      | 0    | 0.5  | VDC  | Low                          |

| 26  | I   | ROW3                            | CMT Keys Row3, Lid closed, | 2.1  | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 | Base band powered          |      | 0    | 0.5  | VDC  | Low                          |

| 27  | Т   | ROW2                            | CMT Keys Row2, Lid closed, | 2.1  | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 | Base band powered          |      | 0    | 0.5  | VDC  | Low                          |

| 28  | Т   | ROW1                            | CMT Keys Row1, Lid closed, | 2.1  | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 | Base band powered          |      | 0    | 0.5  | VDC  | Low                          |

| 29  | Т   | ROW0 CMT Keys Row0, Lid closed, |                            | 2.1  | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 | Base band powered          |      | 0    | 0.5  | VDC  | Low                          |

| 30  | 0   | COL4                            | CMT Keys Col4              | 2.1  | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.5  | VDC  | Low                          |

| 31  | 0   | COL3                            | CMT Keys Col3              | 2.1  | 2.80 | 2.85 | VDC  | High                         |

|     |     |                                 |                            |      | 0    | 0.5  | VDC  | Low                          |

Table 4. UI flex Connector X800 (continued)

BS1

| Table 4. UT flex Connector X800 (continued) |     |          |                               |     |      |      |      |                                    |  |

|---------------------------------------------|-----|----------|-------------------------------|-----|------|------|------|------------------------------------|--|

| Pin                                         | I/O | Name     | Function                      | Min | Nom  | Max  | Unit | Description /<br>Note              |  |

| 32                                          | 0   | COL2     | CMT Keys Col2                 | 2.1 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.5  | VDC  | Low                                |  |

| 33                                          | 0   | COL1     | CMT Keys Col1                 | 2.1 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.5  | VDC  | Low                                |  |

| 34                                          | 0   | COL0     | CMT Keys Col0                 | 2.1 | 2.80 | 2.8  | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.5  | VDC  | Low                                |  |

| 35                                          | Т   | APP_ROW1 | PDA Application row1          | 2.0 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.8  | VDC  | Low                                |  |

| 36                                          | Т   | APP_ROW0 | PDA Application row0          | 2.0 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.8  | VDC  | Low                                |  |

| 37                                          | 0   | APP_COL3 | PDA Application col3          | 2.3 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.45 | VDC  | Low                                |  |

| 38                                          | 0   | APP_COL2 | PDA Application col2          | 2.3 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.45 | VDC  | Low                                |  |

| 39                                          | 0   | APP_COL1 | PDA Application col1          | 2.3 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.45 | VDC  | Low                                |  |

| 40                                          | 0   | APP_COL0 | PDA Application col0          | 2.3 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.45 | VDC  | Low                                |  |

| 41                                          | 0   | LCDCD    | CMT LCD driver command/       | 2.1 | 2.80 | 2.85 | VDC  | High, data                         |  |

|                                             |     |          | data selection                |     | 0    | 0.5  | VDC  | Low, command                       |  |

| 42                                          | 0   | LCDSCx   | CMT LCD driver chip select    | 2.1 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.5  | VDC  | Low, chip selected                 |  |

| 43                                          |     | GND      | Global Ground                 |     |      |      |      |                                    |  |

| 44                                          | 0   | GENSCLK  | CMT LCD driver bus clock      | 2.1 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.5  | VDC  | Low                                |  |

|                                             |     |          |                               |     |      | 4.0  | MHz  |                                    |  |

| 45                                          |     | GND      | Global Ground                 |     |      |      |      |                                    |  |

| 46                                          | 0   | GENSDIO  | CMT LCD driver serial data    | 2.1 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.5  | VDC  | Low                                |  |

|                                             |     |          |                               |     |      | 4.0  | MHz  |                                    |  |

| 47                                          |     | GND      | Global Ground                 |     | •    |      |      |                                    |  |

| 48                                          | 0   | LCDRST   | CMT LCD Reset                 | 2.1 | 2.80 | 2.85 | VDC  | High                               |  |

|                                             |     |          |                               |     | 0    | 0.5  | VDC  | Low                                |  |

| 49                                          |     | VBB      |                               | 2.7 | 2.8  | 2.85 | VDC  |                                    |  |

| 50                                          | I   | PWRKEY   | CMT Power switch              | 2.1 | 2.80 | 2.85 | VDC  | Inactive state                     |  |

|                                             |     |          |                               |     | 0    | 0.45 | VDC  | L(Pulse)=Power<br>on/off, min 64ms |  |

| 51                                          |     | VPDA     | Filtered battery voltage from | 3.0 | 3.6  | 4.1  | V    |                                    |  |

|                                             |     |          | PDA                           |     | 0    |      | mA   | PDA and CMT backlights off         |  |

|                                             |     |          |                               | 40  |      | 65   | mA   | PDA LCD back-<br>light ON          |  |

|                                             |     |          |                               | 10  |      | 20   | mA   | PDA LCD back-<br>light OFF         |  |

Table 4. UI flex Connector X800 (continued)

# Board to board connector signals

All interfaces from the BS8 module to the BS1 module are fed over a 50–pin board-to-board connector.

The function of the Interface is to transfer the battery voltage from the BS8 module, and transfer data between the BS8, BS2, and BS1 modules.

The signal definition and the most significant specifications of signals are collected in the next table.

| Pin | I/O | Name    | Function                                               | Min  | Nom   | Мах  | Unit | Description /<br>Note               |

|-----|-----|---------|--------------------------------------------------------|------|-------|------|------|-------------------------------------|

| 1   |     | VBATT   | Battery Positive                                       | 3.0  | 3.6   | 4.1  | V    | Unregulated Bat-<br>tery Voltage    |

| 2   |     |         |                                                        | 0.3  |       | 1000 | mA   | Current from BS8                    |

| 3   |     |         |                                                        |      |       |      |      | module                              |

| 4   |     |         |                                                        |      |       |      |      |                                     |

| 5   |     |         |                                                        |      |       |      |      |                                     |

| 6   | I   | XEAR    | Audio Output for Handsfree<br>and Car Kit Use          |      |       | 500  | mVpp |                                     |

| 7   |     | GND     | Global Ground                                          |      |       |      |      | Reference for oth-<br>er signals    |

| 8   | Т   | BATTDET | Battery Position Information                           | 2.0  | 2.80  | 2.85 | VDC  |                                     |

|     |     |         |                                                        | 0    | 0     | 0.8  | VDC  |                                     |

| 9   | I   | HFENA   | Internal Handsfree Amplifier<br>Control                | 2.1  | 2.80  | 2.85 | VDC  | High, HF amplifier enabled          |

|     |     |         |                                                        |      | 0     | 0.5  | VDC  | Low, HF amplifier disabled          |

| 10  |     | EARP    | Earpiece Positive                                      | 50   |       | 223  | mVpp | Differential signal                 |

| 11  |     | EARN    | Earpiece Negative                                      |      |       |      |      |                                     |

| 12  |     | GND     | Global Ground                                          |      |       |      |      |                                     |

| 13  | 0   | PWRONx  | PDA start baseband to ser-<br>vice Request State (SRS) | 2.30 | 2.8   | 2.85 | VDC  | High                                |

|     |     |         | Vice Request State (SRS)                               |      | 0     | 0.45 | VDC  | Low, powering up the CMT            |

| 14  | 0   | 32kHz   | Sleep clock for the CMT                                | 2.30 | 2.8   | 2.85 | VDC  | high                                |

|     |     |         |                                                        |      | 0     | 0.45 | VDC  | low                                 |

|     |     |         |                                                        |      |       | 12   | mA   | Maximum current for PDA             |

|     |     |         |                                                        |      | 32768 |      | Hz   | Pulse frequency                     |

|     |     |         |                                                        | 20   | 50    | 80   | %    | Duty cycle                          |

|     |     |         |                                                        |      |       | 1    | %    | Jitter                              |

| 15  |     | GND     | Global Ground                                          |      |       |      |      |                                     |

| 16  |     | VBB     | CMT System Power                                       | 2.7  | 2.8   | 2.85 | VDC  | Regulated CMT baseband voltage      |

|     |     |         |                                                        |      |       | 1    | mA   | Maximum current                     |

| 17  | 0   | PWRKEYx | CMT Power Switch                                       | 2.0  | 2.80  | 2.85 | VDC  | Inactive state                      |

|     |     |         |                                                        |      | 0     | 0.45 | VDC  | L(Pulse)=Power<br>on/off, min. 64ms |

Table 5. Board to board connector X830

RAE-2

|     | Table 5. Board to board connector x650 (continued) |           |                          |      |       |      |      |                                 |

|-----|----------------------------------------------------|-----------|--------------------------|------|-------|------|------|---------------------------------|

| Pin | I/O                                                | Name      | Function                 | Min  | Nom   | Max  | Unit | Description /<br>Note           |

| 18  | Ι                                                  | CMT_BL_ON | CMT UI Light On          | 2.1  | 2.8   | 2.85 | VDC  | High, backlight en-<br>abled    |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low                             |

| 19  | 0                                                  | ROW3      | CMT Keys Row 3           | 2.5  | 2.8   | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.2  | VDC  | Low                             |

| 20  | 0                                                  | ROW2      | CMT Keys Row 2           | 2.5  | 2.8   | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.2  | VDC  | Low                             |

| 21  | 0                                                  | ROW1      | CMT Keys Row 1           | 2.5  | 2.8   | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.2  | VDC  | Low                             |

| 22  | 0                                                  | ROW0      | CMT Keys Row 0           | 2.5  | 2.8   | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.2  | VDC  | Low                             |

| 23  |                                                    | GND       | Global Ground            |      |       |      |      |                                 |

| 24  | Ι                                                  | COL4      | CMT Keys Column 4        | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low                             |

| 25  | Ι                                                  | COL3      | CMT Keys Column 3        | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low                             |

| 26  | Ι                                                  | COL2      | CMT Keys Column 2        | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low                             |

| 27  | Ι                                                  | COL1      | CMT Keys Column 1        | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low                             |

| 28  | Ι                                                  | COL0      | CMT Keys Column 0        | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low                             |

| 29  |                                                    | GND       | Global Ground            |      | •     | •    | •    |                                 |

| 30  | Ι                                                  | LCDCD     | CMT LCD Command / Data   | 2.1  | 2.80  | 2.85 | VDC  | High, data                      |

|     |                                                    |           | Select                   |      | 0     | 0.5  | VDC  | Low, command                    |

| 31  | Ι                                                  | LCDRSTx   | CMT LCD Reset            | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low, LCD reset                  |

| 32  | Ι                                                  | LCDCSx    | CMT LCD Chip Select      | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low, chip selected              |

| 33  |                                                    | GND       | Global Ground            |      | •     |      |      |                                 |

| 34  | Ι                                                  | GENSCLK   | CMT LCD and CCONT Serial | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           | Clock                    |      | 0     | 0.5  | VDC  | Low                             |

|     |                                                    |           |                          |      | 3.250 |      | MHz  | Pulse frequency in active state |

| 35  | Ι                                                  | GENSDIO   | CMT LCD and CCONT Serial | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           | Data                     |      | 0     | 0.5  | VDC  | Low                             |

|     |                                                    |           |                          |      | 1.625 |      | MHz  | Maximum pulse<br>frequency      |

| 36  |                                                    | GND       | Global Ground            |      |       |      |      |                                 |

| 37  | 0                                                  | FBUS_RXD  | Fast Serial Data to CMT  | 2.30 | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.45 | VDC  | Low                             |

| 38  | Ι                                                  | FBUS_TXD  | Fast Serial Data to PDA  | 2.1  | 2.80  | 2.85 | VDC  | High                            |

|     |                                                    |           |                          |      | 0     | 0.5  | VDC  | Low                             |

|     |                                                    |           |                          |      |       |      |      |                                 |

Table 5. Board to board connector X830 (continued)

|     | Table 5. Board to board connector X830 (continued) |            |                                                              |      |       |      |       |                                                                                                  |

|-----|----------------------------------------------------|------------|--------------------------------------------------------------|------|-------|------|-------|--------------------------------------------------------------------------------------------------|

| Pin | I/O                                                | Name       | Function                                                     | Min  | Nom   | Мах  | Unit  | Description /<br>Note                                                                            |

| 39  |                                                    | GND        | Global Ground                                                |      |       | _    |       |                                                                                                  |

| 40  | I/O                                                | MBUS       | Bidirectional Serial Bus                                     | 2.30 | 2.80  | 2.85 | VDC   | High, to the CMT                                                                                 |

|     |                                                    |            |                                                              |      | 0     | 0.45 | VDC   | Low, to the CMT                                                                                  |

|     |                                                    |            |                                                              | 2.1  | 2.80  | 2.85 | VDC   | High, from the CMT                                                                               |

|     |                                                    |            |                                                              |      | 0     | 0.5  | VDC   | Low, from the CMT                                                                                |

| 41  |                                                    | VSYS       | PDA System voltage                                           | 2.75 | 2.80  | 2.85 | VDC   |                                                                                                  |

|     |                                                    |            |                                                              |      |       | 2    | mA    |                                                                                                  |

| 42  | 0                                                  | LIDSWITCH  | Lid State Information                                        | 2.75 | 2.80  | 2.85 | VDC   | High, Cover open                                                                                 |

|     |                                                    |            |                                                              |      | 0     |      | VDC   | Low, Cover closed                                                                                |

|     |                                                    |            |                                                              |      | 10    |      | kohm. | Pull–up resistor                                                                                 |

| 43  | I                                                  | MMC_SWITCH | MMC Cover State Information                                  | 2.75 | 2.80  | 2.85 | VDC   | High, Cover open                                                                                 |

|     |                                                    |            |                                                              |      | 0     |      | VDC   | Low, Cover closed                                                                                |

| 44  |                                                    | GND        | Global ground                                                |      | •     |      | •     |                                                                                                  |

| 45  | 45 I/O                                             | D MMC_CMD  | O MMC_CMD MMC Command / Address /<br>Response, Bidirectional | 2.30 | 2.80  | 2.85 | VDC   | Data to the card<br>High, Pulled up<br>with 10kohm resis-<br>tor to MMC_VSYS<br>in CMT Module    |

|     |                                                    |            |                                                              |      | 0     | 0.45 | VDC   | Data to the Card<br>Low                                                                          |

|     |                                                    |            |                                                              | 2.1  | 2.80  | 2.85 | VDC   | data from the card<br>High, Pulled up<br>with 10kohm resis-<br>tor to MMC_VSYS<br>in CMT Module  |

|     |                                                    |            |                                                              |      |       | 0.34 | VDC   | Data from the card<br>Low                                                                        |

|     |                                                    |            |                                                              |      | 259.3 |      | kHz   | frequency                                                                                        |

| 46  |                                                    | MMC_VSYS   | MMC Power Supply                                             | 2.75 |       | 2.85 | VDC   |                                                                                                  |

|     |                                                    |            |                                                              | 0.01 |       | 100  | mA    | Current                                                                                          |

| 47  | I/O                                                | MMC_DATA   | MMC Bidirectional Data                                       | 2.30 | 2.80  | 2.85 | VDC   | Data to the Card<br>High, Pulled up<br>with 10kohm resis-<br>tor to MMC_VSYS<br>in CMT Module    |

|     |                                                    |            |                                                              |      | 0     | 0.45 | VDC   | Data to the card<br>Low                                                                          |

|     |                                                    |            |                                                              | 2.1  | 2.80  | 2.85 | VDC   | Data from the<br>Card High, Pulled<br>up with 10kohm<br>resistor to<br>MMC_VSYS in<br>CMT Module |

|     |                                                    |            |                                                              |      | 0     | 0.34 | VDC   | Data from the card<br>Low                                                                        |

|     |                                                    |            |                                                              |      | 8.294 |      | MHz   | frequency                                                                                        |

| 48  |                                                    | GND        | Global ground                                                |      |       |      |       |                                                                                                  |

#### Table 5. Board to board connector X830 (continued)

BS1

| Pin | I/O | Name    | Function      | Min    | Nom  | Мах   | Unit | Description /<br>Note |

|-----|-----|---------|---------------|--------|------|-------|------|-----------------------|

| 49  | 0   | MMC_CLK | MMC Clock     | 2.30   | 2.80 | 2.85  | VDC  | High                  |

|     |     |         |               |        | 0    | 0.45  | VDC  | Low                   |

|     |     |         |               | 0.2592 |      | 8.294 | MHz  | Frequency             |

| 50  |     | GND     | Global Ground |        |      |       |      |                       |

Table 5. Board to board connector X830 (continued)

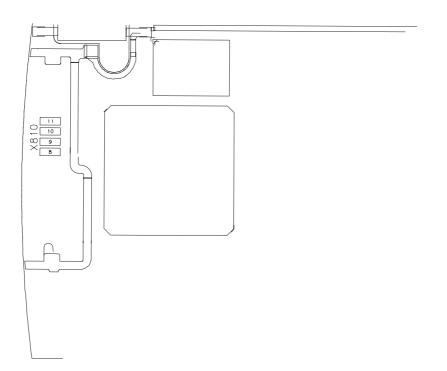

#### System connector pads

The RAE–2 System connector is a multipurpose connector, which is shared with the BS8 module. In this section are described only the signals that are connected to the BS1 module. These signals are needed for PC–connectivity. The connector comprises spring type contacts to the BS1 and BS8 module. The PCB comprises pads on which the springs are pressed.

| Pin | Line<br>Symbol | Parameter        | Minimum | Nominal | Maximum | Unit | Unit / Notes |

|-----|----------------|------------------|---------|---------|---------|------|--------------|

| 8   | DCT_TX         | PDA CPU Receive  | 2.0     | 2.80    | 2.85    | VDC  |              |

|     |                | data             | 0       |         | 0.8     | VDC  |              |

| 9   | DCE_RX         | PDA CPU Transmit | 2.30    | 2.80    | 2.85    | VDC  |              |

|     |                | data             | 0       |         | 0.45    | VDC  |              |

| 10  | DCE_DTR        | PDA CPU Data set | 2.0     | 2.80    | 2.85    | VDC  |              |

|     |                | ready            | 0       |         | 0.8     | VDC  |              |

| 11  | GND            | Global ground    |         |         |         |      |              |

## Audio connector pads

The audio connector has two contact types. The earpiece contacts are of spring type, and the contacts for the handsfree speaker are elastomeric contacts.

| Pin  | Line<br>Symbol | Parameter                          | Minimum | Nominal | Maximum | Unit | Unit / Notes                                                                            |

|------|----------------|------------------------------------|---------|---------|---------|------|-----------------------------------------------------------------------------------------|

| E850 | EARP           | Earpiece positive node             | 50      |         | 223     | mVpp | Differential voltage between<br>EARP and EARN nodes                                     |

| E851 | EARN           | Earpiece negative node             |         |         |         |      |                                                                                         |

| E880 | PHFEARN        | Handsfree speaker<br>negative node |         |         | 6.0     | Vpp  | VBATT=4.4V. Differential volt-<br>age between PHFEARN and<br>PHFEARP nodes              |

|      |                |                                    |         |         | 4.4     | Vpp  | VBATT=3.6V. Differential volt-<br>age between PHFEARN and<br>PHFEARP nodes              |

| E881 | PHFEARP        | Handsfree speaker<br>positive node |         |         | 6.0     | Vpp  | VBATT=4.4V. Differential volt-<br>age between PHFEARN and<br>PHFEARP nodes              |

|      |                |                                    |         |         | 4.4     | Vpp  | VBATT=3.6VBATT=4.4V. Dif-<br>ferential voltage between<br>PHFEARN and PHFEARP<br>nodes. |

Table 7. Audio connector pads

## Backup battery

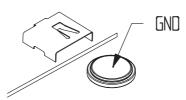

Figure 2. Backup battery insertion direction

NOTE: Positive node is against PCB, it can be identified by 2mm diameter contact plate

Table 8. Backup battery holder X450

| Pin | Name                         | Function | Min | Nom | Мах | Unit | Description / Note |

|-----|------------------------------|----------|-----|-----|-----|------|--------------------|

|     | VBACK Backup battery voltage |          | 2.4 | 3.0 | 3.1 | VDC  |                    |

|     | GND Global ground            |          |     |     |     |      |                    |

# **Internal Signals and Connections**

| Pin | Line<br>Symbol | Parameter              | Minimum | Nominal | Maximum | Unit / Notes |

|-----|----------------|------------------------|---------|---------|---------|--------------|

| 3   | TXD            | Transmit data from CPU | 2.30V   | 2.80V   | 2.85V   |              |

|     |                |                        |         | 0V      | 0.45V   |              |

| 4   | RXD            | Receive data to CPU    | 2.0V    | 2.8V    | 2.85V   |              |

|     |                |                        |         | 0       | 0.8V    |              |

#### Table 9. IR-transceiver (N300) signals

#### Table 10. Signals between PDA CPU and Flash memories

| Name       | Function                     | Min  | Nom  | Max  | Unit | Description / Note |

|------------|------------------------------|------|------|------|------|--------------------|

| SA(21:1)   | System address               | 2.30 | 2.80 | 2.85 | VDC  | High               |

|            |                              |      | 0    | 0.4  | VDC  | Low                |

| SD(15:0)   | System data from CPU         | 2.30 | 2.8  | 2.85 | VDC  | High               |

|            |                              |      | 0    | 0.4  | VDC  | Low                |

|            | System data from memory      | 2.40 | 2.8  | 2.85 | VDC  | High               |

|            |                              |      | 0    | 0.4  | VDC  | Low                |

| ROMCS(2:0) | Chip selects for Flash memo- | 2.30 | 2.80 | 2.85 | VDC  | High               |

|            | ries                         |      | 0    | 0.4  | VDC  | Low                |

| FLSHWRx    | Flash write signal           | 2.30 | 2.80 | 2.85 | VDC  | High               |

|            |                              |      | 0    | 0.4  | VDC  | Low, write enabled |

| ROMRDx     | Flash read signal            | 2.30 | 2.80 | 2.85 | VDC  | High               |

|            |                              |      | 0    | 0.4  | VDC  | Low, read enabled  |

| GPIO_CS1   | Write protect for RFD memory | 2.30 | 2.80 | 2.85 | VDC  | High               |

|            |                              |      | 0    | 0.4  | VDC  | Low, powered down  |

| GPIO_CS7   | RFD Flash ready              | 2.0  | 2.80 | 2.85 | VDC  | High, ready        |

|            |                              |      | 0    | 0.8  | VDC  | Low, busy          |

#### Table 11. Signals between PDA CPU and DRAM Memory

| Name     | Function                      | Min  | Nom  | Max  | Unit | Description / Note |

|----------|-------------------------------|------|------|------|------|--------------------|

| MA(11:0) | Memory address                | 2.30 | 2.80 | 2.85 | VDC  | High               |

|          |                               |      | 0    | 0.4  | VDC  | Low                |

| SD(15:0) | SD(15:0) Memory data from CPU |      | 2.8  | 2.85 | VDC  | High               |

|          | Memory data from memory       |      | 0    | 0.4  | VDC  | Low                |

|          |                               |      | 2.8  | 2.85 | VDC  | High               |

|          |                               | 0    | 0    | 0.6  | VDC  | Low                |

| RAS0     | Row access strobe             | 2.30 | 2.80 | 2.85 | VDC  | High               |

|          |                               |      | 0    | 0.4  | VDC  | Low                |

| CAS(1:0) | Column access strobe          | 2.30 | 2.80 | 2.85 | VDC  | High               |

|          |                               |      | 0    | 0.4  | VDC  | Low                |

| MWEx     | Memory write enable           | 2.30 | 2.80 | 2.85 | VDC  | High               |

|          |                               |      | 0    | 0.4  | VDC  | Low, write enabled |

BS1

| Name    | Function                     | Min  | Nom  | Max  | Unit | Description / Note |

|---------|------------------------------|------|------|------|------|--------------------|

| SA(2:0) | System address               | 2.30 | 2.80 | 2.85 | VDC  | High               |

|         |                              |      | 0    | 0.4  | VDC  | Low                |

| SD(6:0) | System data                  | 2.40 | 2.8  | 2.85 | VDC  | High               |

|         |                              |      | 0    | 0.4  | VDC  | Low                |

| CS3x    | Chip select for Phaser       | 2.30 | 2.80 | 2.85 | VDC  | High               |

|         |                              |      | 0    | 0.4  | VDC  | Low                |

| IOWx    | Phaser write signal          | 2.30 | 2.80 | 2.85 | VDC  | High               |

|         |                              |      | 0    | 0.4  | VDC  | Low, write enabled |

| IORx    | Phaser read signal           | 2.30 | 2.80 | 2.85 | VDC  | High               |

|         |                              |      | 0    | 0.4  | VDC  | Low, read enabled  |

| RESETx  | Reset for CPU, and for Flash | 2.30 | 2.80 | 2.85 | VDC  | High               |

|         | memories.                    |      | 0    | 0.4  | VDC  | Low                |

| VBACK   | Back-up battery voltage      | 2.40 | 3.0  | 3.1  | VDC  | High               |

| V17_EN  | LCD bias voltage enable      | 2.30 | 2.80 | 2.85 | VDC  | High               |

|         |                              |      | 0    | 0.4  | VDC  | Low                |

| V28_1EN | LCD logic voltage enable     | 2.30 | 2.80 | 2.85 | VDC  | High               |

|         |                              |      | 0    | 0.4  | VDC  | Low                |

| Table 12. Signals between PDA CPU and PWRU | Table 12. | Signals | between | PDA | CPU | and | PWRU |

|--------------------------------------------|-----------|---------|---------|-----|-----|-----|------|

|--------------------------------------------|-----------|---------|---------|-----|-----|-----|------|

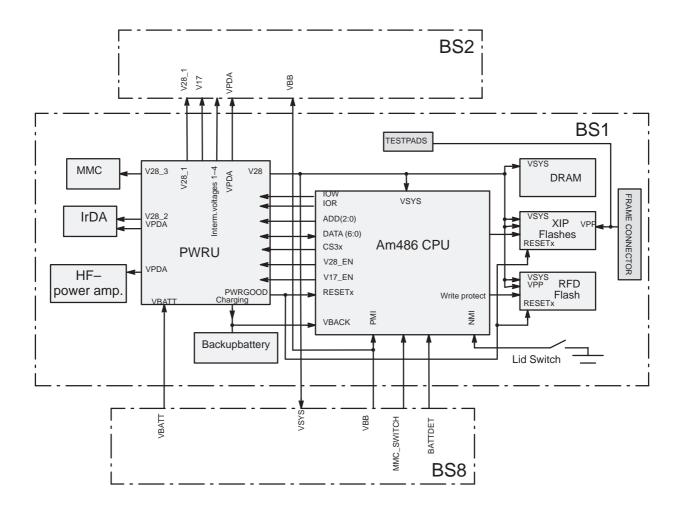

# **Functional Description**

# **Power Unit**

Figure 3. PDA Power distribution diagram

Battery voltage is supplied from the BS8 module through a board to board connector. In the BS1 module the battery voltage is filtered and then supplied to the Phaser, IR-transceiver circuit, BS2 module, and PHF-speaker circuitry.

The phaser generates internally the system voltage V28, switched voltages V28\_1,V28\_2, V28\_3, the LCD bias voltage V17, the LCD intermediate voltages V17\_ix, x=1-4 and the backup battery charging voltage VBACK.

When the battery voltage level is adequate, the PWRU switches V28 on and after a certain time releases the reset–signal for the CPU. The CPU

controls the LCD, MMC, and IR-transceiver logic voltages by writing command to the PWRU register. Optionally the CPU can control the LCD logic- and biasing voltage directly by means of I/O signals.

The backup battery supplies power to the CPU's real time clock. The PWRU charges the backup battery when the main battery is connected. The CPU puts the Flash memories to power down mode when they are not used.

The BS8 signal BATTDET is a warning signal that the battery will be removed soon, when power down procedure is started. VBB is the supply voltage for the CMT display, located in the BS2 module, and the VBB provides information for the BS1 CPU whether the CMT powered or not and it enables the keyboard buffer. The MMC\_SWITCH indicates that the MMC card will be removed, when the CPU controls the Phaser to turn the V28\_3 off.

#### Input filter

The Battery voltage is fed from the BS8 module and then filtered by using a LC–lowpass filter, after filtering the voltage is named VPDA. The VPDA is then fed to the PWRU, the IR–transceiver, the PHF–speaker circuitry, and to the BS2 module.

#### Linear regulator V28

System voltage V28 is generated by a linear regulator. V28 stays on all the time when the battery voltage is higher than cutoff limit.

#### Linear regulator V28\_1,\_2,\_3

These regulators are controlled by the CPU. The CPU can enable these regulators by writing a command to the PWRU's register. V28\_1 is the switched V28 and is used for the LCD logic. V28\_2 is the switched V28 and is used for the IRDA logic. V28\_3 is the MMC voltage.

#### Switchmode regulator V17

The LCD bias voltage V17 is generated by a step–up DC–DC converter. The control scheme is the current limited pulse width modulation (PWM). The switching transistor is internal. The regulator output, too, is separated from the battery line by an integrated switch transistor between the regulator output and load.

#### **Backup battery**

The Real time clock is kept running by a backup battery only when the main battery is not connected. At the nominal RTC load used , the 12mAh capacity of the backup battery provides about 40 days of RTC operation when the main battery is not connected. The backup battery is

rechargeable. It is charged by the Phaser VBACK regulator using 0.5mA current when the main battery is connected.

#### Reset and power management

The Phaser is connected to the I/O space of the H3 by using a 7 bit wide data bus and a 3 bit wide address bus. The BS2 PDAPWRU on the PDA board supplies two different voltage levels to the system; 2.85V is used as the main operating voltage for all circuits and about 19V that is needed for the LCD bias (V17). The LCD bias voltage is used to adjust the contrast ratio of the LCD screen. The LCD bias voltage is controlled by the Phaser ASIC.

The V17 and V28\_1 ON/OFF are switched by the Phaser, but optionally also the CPU can control these signals directly with HW means, independently of the SW controlled register settings. The phaser provides also the POWERGOOD signal for the CPU. The system reset circuit is part of the power supply. When the battery voltage is higher than 3.4V a PWRGOOD is generated for the CPU. The reset circuit also asserts the reset signal whenever the Vcc supply voltage declines below the threshold, keeping it asserted for at least 50ms after Vcc has risen above the reset threshold. The reset circuit is designed to ignore fast transients (t <  $64\mu$ s) in Vcc.

There is an undervoltage lockout (UVLO) block inside the Phaser. Below the threshold limit the comparator shuts down all Phaser functionality to prevent the battery from overdischarge. Otherwise the VSYS regulator current drains the battery when left unused for long period. After the UVLO there is only reference block in the Phaser drawing current from the battery. The UVLO has a little hysteresis and is cancelled when the battery voltage has risen to 2.7V. However, reset to the CPU is given only when battery voltage rises to 3.45V. This in order to avoid unsuccessful power–ups. When the lockout voltage level is reached, the battery voltage rises because the load is removed.

# PDA CPU

The PDA CPU is a SC450–33CC in a 256 pin plastic ball grid array package.

The core features a 32-bit architecture with internal 8k write-back cache. The clock rate is 33MHz, which can be slowed down to1MHz. The default clock rate on reset is 8.29MHz. The bus clock rate is 33MHz. A 32kHz clock signal for the BS8 module is provided by the CPU PLL circuit. The clock signal is started when ever the system voltage is applied to the CPU.

The CORE starts when the reset signal is provided and then it begins to execute the program code from the Flash memory. The external pull–up resistor controls the start–up procedure (Boot code Chip select, and data bus width).

The memory controllers are integrated to the chip. A ROM controller is used for Flash interface and a DRAM controller supports extended data out (EDO) page mode DRAMs. Both memory types (DRAM and Flash) have their own address and data bus routed directly to the CPU. The power unit is controlled via an I/O-mapped 7-bit wide data- and 3-bit wide address bus, which is shared with Flash data- and address bus. The CPU block diagram is the figure below.

For serial interface two UART circuits are used. UART2 is a serial interface reserved for data transfer between the BS1 and BS8 modules. UART2 is disabled or enabled according to the CMT voltage. UART1 is used for RS–232 interface with external level changer. The UARTs can be connected together to establish Re–Link connection, where received data is directly linked to the UART's transmit data pin. That way the BS8 module can be programmed by using an external RS-interface. Autobauding detection circuitry is included in the UART1 block. The LCD–controller supports a 4-bit data and 16-grey shades. The display control signals are routed from the CPU. The bigger (640x200) LCD is located in the lid. The interconnection between the CPU and the LCD comprises a flex through the hinge. Data and control signals are provided by the CPU. The required voltages are supplied by the PWRU.

The PDA CPU supports a synchronous serial interface that is compatible with the Multimedia Card Bus (MMC) Protocol. The MMC is changeable Flash or ROM memory card with variable memory size. The MMC connector is located on the BS8 Module. MMC signals are routed to the BS8 module through a Board to board connector. The interface consists of three pins: one clock(output), one command/response (bidirectional), and one data pin (bidirectional). The controller is capable up to 8Mbits/second transfer rate.

The keyboard controller includes a matrix keyboard which is used for PDA keyboard and for PDA lid keys. The PC/AT standard core includes a 8254 programmable interval timer, two 8259 programmable interrupt controllers, and a real time clock. The CPU's general purpose input/outputs (GPIO) are controlled by the CPU's registers.

# I/O Signals

In the Table 13 below are listed BS1 module I/O signals which are mapped to general purpose pins of the CPU.

| Scotty Pin | Signal Name | Low                                            | High                           | Note                                                                                      |

|------------|-------------|------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------|

| GPIO_CS1   | RFD_WPx     | Write operation                                | Write not possible             |                                                                                           |

| GPIO_CS2   | XIP_STS     | Memory busy                                    | Memory ready                   | Input, CS(1:0) Flash memory status                                                        |

| GPIO_CS5   | TESTMODEx   | Testmode acti-<br>vated                        | Reset, Suspend,<br>Operation   | Input.                                                                                    |

| GPIO_CS6   | PWRONx      | Powering the<br>CMT up                         | Reset, Suspend                 | Activate the power on procedure for the CMT                                               |

| GPIO_CS7   | Flash_RDY   | Flash performing<br>an internal opera-<br>tion | Flash ready for<br>new command | Input. Open drain output, processor's internal pull–up is used. (Only for the RFD)        |

| GPIO_CS8   | MMC_Switch  | MMC cover<br>closed                            | Reset, MMC cov-<br>er open     | Input. MMC cover status indication                                                        |

| GPIO_CS9   | MBUS        |                                                |                                | Output during BS8 Flashing from BS1 module, Input otherwise.                              |

| GPIO_CS11  | Phaser_CSx  | Chip Selected                                  | Chip not selected              | Output.                                                                                   |

| GPIO_CS12  | VBB         | CMT off                                        | Reset, CMT on                  | Input.                                                                                    |

| GPIO_CS13  |             |                                                |                                |                                                                                           |

| GPIO16     | LCDBL_EN    | Reset, Suspend,<br>BL disabled                 | Backlight acti-<br>vated       | Backlight EL driver controller.                                                           |

| GPIO18     | BZR_EN      | Reset, Suspend                                 | Operation                      | Enables the PA.                                                                           |

| BL1        | BATTDET     | Battery con-<br>nected                         | Battery removed                | Indicates when the battery is going to<br>be removed. Pin has build in 15ms de-<br>bounce |

| SUS/RES    | LIDSWITCH   | Cover closed                                   | Cover open                     | STI. Indicates when the coved is open or closed                                           |

Table 13. Spock CPU Controllable I/O Signals

BS1

| LVDD | LVDD | · · ·          | PDA LCD Logic voltage activated   | Routed to the Phaser |

|------|------|----------------|-----------------------------------|----------------------|

| LVEE | LVEE | Reset, Suspend | PDA LCD bias<br>voltage activated | Routed to the Phaser |

## **Memories**

The memory units of the module are connected to the CPU via a 16–bit wide data bus. Both memory types (DRAM and Flash) have an own data– and address bus.

#### **DRAM** memory

The 1Mx16bit DRAM is connected to the CPU with a dedicated 16–bit wide data- and 12-bit wide address bus. The DRAM type used is the extended data out (EDO) DRAM with 60ns access time, and self–refresh capability. DRAM is packaged in a 5.55mmX9.10mm, 40–ball uBGA package.

When the DRAM is driven by the CPU, no wait states is needed.

#### Flash memory

Three 1Mx16bit Flash memory devices are used for non–volatile memory. The Flash type features a 120ns access time. The Flash is packaged in 8mmX11mm 64–ball CSP package. When the Flash is read by the CPU, 4 wait states are needed to ensure proper timing.

# **External Serial Interface**

The UART1 External serial interface is used for PC–connectivity. The RS– connection is provided by a 3–signal interface (RXD,TXD, and DTR) which is routed to the system connector. Maximum data rate is 230.4kbps.

The re–link feature connects the UART1 and the UART2 (FBUS) internally together. This provides the signal routing from the system connector to the CMT.

The Autobaud detection circuitry can detect bit rates from 300 bps tp 115.2kbps. The autobaud state machine starts when enabled by the CPU. The bit rate measurement begins on the first negative edge of the CPU\_RXD line. After detecting the start bit width, and therefore the bit rate, the remainder of the incoming data stream is sampled at this rate.

This UART is shared with the IrDA circuitry and thus only one of them can be used at a time.

# **IR**–Transceiver

The IR-transceiver controller is shared with the UART1. Infrared data transfer is started with 9600bps and then the data rate is increased to 115.2kbps if the connected device supports higher speed. The protocol is the standard one of the Infrared Data Association. The CPU hardware implementation includes bit stuffing (when transmitting), CRC calculation, removing bit stuffing, and removing beginning of frame (when receiving).

# Handsfree loudspeaker

The Handsfree speaker power amplifier circuitry is located on the BS1 module. The HF–speaker is used to produce the PDA key–click sounds, error beeps, and tunes. When the lid is opened, the loudspeaker is used as an handsfree speaker, producing key–click sound when a PDA QWERTY key is pressed, and producing tunes. The HF–speaker power amplifier can be controlled by the PDA CPU, or CMT.

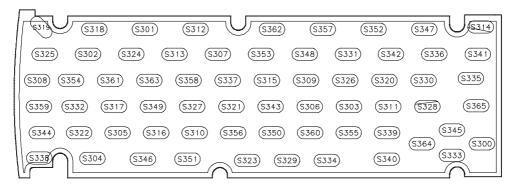

# Keyboard

The keyboard interface comprises 10x8 matrix lines. The QWERTY keyboard pads are located on the other side of the BS1 module board. 4x2 (2Row/4Column) matrix is routed to the lid. Four columns are multiplexed with CMT keyboard columns. Multiplexing is done by using buffer located on the BS1 module. This buffer is controlled by Baseband voltage (VBB). When the lid is closed these four columns are switched to inputs and they are not read by the CPU.

BS1

#### **Technical Documentation**

|      |      |      |      | С    | olumn |      |               |                        |

|------|------|------|------|------|-------|------|---------------|------------------------|

|      | Col0 | Col1 | Col2 | Col3 | Col4  | Col5 | Col6          | Col7                   |

| Row0 | S730 | S732 | S734 | S736 | S331  | S337 |               | S343                   |

| Row1 | S731 | S733 | S735 | S325 | S330  | S336 | S341          | S342                   |

| Row2 | S300 | S318 | S347 | S324 | S335  | S311 | S303          | S305                   |

| Row3 | S306 | S307 | S308 | S327 | S328  | S310 | S309          | S323,<br>S329,<br>S334 |

| Row4 | S312 | S313 | S314 | S332 | S333  | S316 | S315          | S317                   |

| Row5 | S301 | S319 | S320 | S321 | S322  | S348 | S349          | S302                   |

| Row6 | S352 | S353 | S354 | S338 | S339  | S356 | S355          |                        |

| Row7 | S357 | S358 | S359 | S344 | S345  | S361 | S360          | S346                   |

| Row8 | S362 | S363 | S364 | S326 | S351  | S365 | S350          |                        |

| Row9 |      |      |      |      |       |      | S304,<br>S340 |                        |

| Table 14. | <b>Key Reference</b> | Numbers vs. | Senses a | nd Drives. |

|-----------|----------------------|-------------|----------|------------|

|           |                      |             |          |            |

NOTE1: Shift pads has dedicated Sense line (ROW9), These shift pads are connected parallel

NOTE2: Grey shaded switches are located in BS2 module.

Figure 4. BS1 PDA keyboard

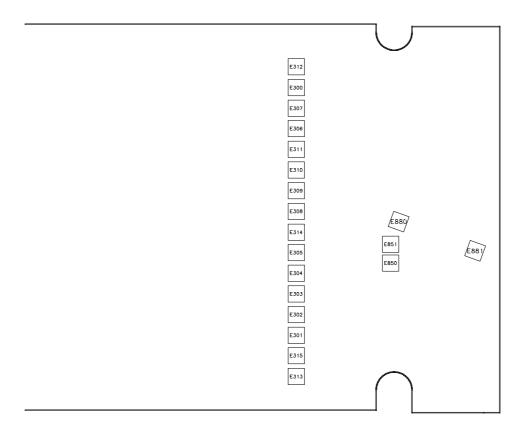

# Test pads

Test pads are located under the battery pack. They include JTAG port which is used for After Sales Flashing purposes. The different voltages can be measured from these testpads. Serial data transfer test pads are used for data transfer between the BS1 and BS8 modules.

Figure 5. Test pad layout

| Pin   | I/O | Name        | Function                             | Min  | Nom  | Мах  | Unit | Description /<br>Note                                   |

|-------|-----|-------------|--------------------------------------|------|------|------|------|---------------------------------------------------------|

| E300  |     | V17_OUT     | PDA LCD Biasing voltage              | 13.8 | 19.4 | 22.2 | VDC  | High                                                    |

|       |     |             |                                      |      | 0    |      | VDC  | Low                                                     |

| E301  | I   | BNDSCN_TMS  | Boundary scan Test mode se-<br>lect  | 2.0  | 2.80 | 2.85 | VDC  | High, test mode selected                                |

|       |     |             |                                      |      | 0    | 0.8  | VDC  | Low                                                     |